# I/O Ports

- Pin direction

- Unidirectional (input or output only)

- Bidirectional (input AND output)

- Data direction register

- Output mode register

- Data register

- Multiple function pins

### 2. ABSOLUTE MAXIMUM RATINGS

| PARAMETER                                                            | CONDITIONS | MIN  | TYP | MAX          | UNITS |

|----------------------------------------------------------------------|------------|------|-----|--------------|-------|

| Ambient temperature under bias                                       |            | -55  |     | 125          | °C    |

| Storage Temperature                                                  |            | -65  |     | 150          | °C    |

| Voltage on any Pin (except VDD and Port I/O) with<br>respect to DGND |            | -0.3 |     | VDD +<br>0.3 | v     |

| Voltage on any Port I/O Pin or /RST with respect to<br>DGND          |            | -0.3 |     | 5.8          | v     |

| Voltage on VDD with respect to DGND                                  |            | -0.3 |     | 4.2          | V     |

| Maximum Total current through VDD, AV+, DGND, and AGND               |            |      |     | 800          | mA    |

| Maximum output current sunk by any Port pin                          |            |      |     | 100          | mA    |

| Maximum output current sunk by any other I/O pin                     |            |      |     | 50           | mA    |

| Maximum output current sourced by any Port pin                       |            |      |     | 100          | mA    |

| Maximum output current sourced by any other I/O pin                  |            |      |     | 50           | mA    |

#### Table 2.1. Absolute Maximum Ratings\*

\* Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### Figure 17.10. P0: Port0 Data Register

| R/W      | R/W                         | R/W                                                                                                   | R/W                       | R/W         | R/W         | R/W           | R/W            | Reset Valu |  |  |  |  |  |

|----------|-----------------------------|-------------------------------------------------------------------------------------------------------|---------------------------|-------------|-------------|---------------|----------------|------------|--|--|--|--|--|

| P0.7     | P0.6                        | P0.5                                                                                                  | P0.4                      | P0.3        | P0.2        | P0.1          | P0.0           | 11111111   |  |  |  |  |  |

| Bit7     | Bit6                        | Bit5                                                                                                  | Bit4                      | Bit3        | Bit2        | Bitl          | Bit0           | SFR Addres |  |  |  |  |  |

|          |                             |                                                                                                       |                           |             |             | (             | bit addressabl | e) 0x80    |  |  |  |  |  |

| Bits7-0: | P0.[7:0]: Port0             | ) Output La                                                                                           | tch Bits.                 |             |             |               |                |            |  |  |  |  |  |

|          |                             | •                                                                                                     |                           | r XBR0, XB  | R1, XBR2, a | and XBR3 R    | legisters)     |            |  |  |  |  |  |

|          | · ·                         | (Write - Output appears on I/O pins per XBR0, XBR1, XBR2, and XBR3 Registers)<br>0: Logic Low Output. |                           |             |             |               |                |            |  |  |  |  |  |

|          | 1: Logic High               | 1: Logic High Output (open if corresponding P0MDOUT.n bit = 0).                                       |                           |             |             |               |                |            |  |  |  |  |  |

|          | (Read - Regard              | dless of XB                                                                                           | R0, XBR1, 2               | XBR2, and X | BR3 Registe | er settings). |                |            |  |  |  |  |  |

|          | 0: P0.n pin is 1            | 0: P0.n pin is logic low.                                                                             |                           |             |             |               |                |            |  |  |  |  |  |

|          | 1: P0.n pin is logic high.  |                                                                                                       |                           |             |             |               |                |            |  |  |  |  |  |

|          | -                           | Note: P0.7 (/WR), P0.6 (/RD), and P0.5 (ALE) can be driven by the External Data Memory Interfac       |                           |             |             |               |                |            |  |  |  |  |  |

|          | -<br>Nata: <b>D</b> 0.7 (/W | D) DO 6 //                                                                                            | D)                        | 5 (ALE)     | h           | de a Eastanna | Dete Mare      | T          |  |  |  |  |  |

|          | 5                           | 2                                                                                                     | <i>2</i> -                | 3 P         | -           |               |                | -          |  |  |  |  |  |

|          | See Section "]              | l6. EXTER                                                                                             | NAL DATA                  | MEMORY      | INTERFA     | CE AND O      | N-CHIP X       | RAM" on    |  |  |  |  |  |

|          | 5                           | 16. EXTER                                                                                             | NAL DATA<br>ation. See al | MEMORY      | INTERFA     | CE AND O      | N-CHIP X       | RAM" on    |  |  |  |  |  |

#### Figure 17.11. P0MDOUT: Port0 Output Mode Register

| R/W      | R/W                              | R/W         | R/W          | R/W          | R/W  | R/W       | R/W        | Reset Value   |

|----------|----------------------------------|-------------|--------------|--------------|------|-----------|------------|---------------|

|          |                                  |             |              |              |      |           |            | 00000000      |

| Bit7     | Bit6                             | Bit5        | Bit4         | Bit3         | Bit2 | Bitl      | Bit0       | SFR Address:  |

|          |                                  |             |              |              |      |           |            | 0xA4          |

| Bits7-0: | P0MDOUT.[7:                      | -           | -            |              |      |           |            |               |

|          | 0: Port Pin out                  |             | 0            | -            |      |           |            |               |

|          | 1: Port Pin out                  | put mode is | s configured | as Push-Pull |      |           |            |               |

| Note:    | SDA, SCL, and<br>configured as ( |             |              |              |      | hen UART1 | is in Mode | 0) are always |

# **Timer Operation**

- Timer mode

- Timer clock source

- Timer output

- Links to other devices

### Timer modes

- Timer

- Counter

- Baud rate generator

- ADC clock generator

- Bus clock generator

| Timer 0 and Timer 1:     | Timer 2:                  | Timer 3:                | Timer 4                   |

|--------------------------|---------------------------|-------------------------|---------------------------|

| 13-bit counter/timer     | 16-bit counter/timer with | 16-bit timer with auto- | 16-bit counter/timer with |

| 15-on counter/inner      | auto-reload               | reload                  | auto-reload               |

| 16-bit counter/timer     | 16-bit counter/timer with |                         | 16-bit counter/timer with |

| 10-bit counter/timer     | capture                   |                         | capture                   |

| 8-bit counter/timer with | Baud rate generator for   |                         | Baud rate generator for   |

| auto-reload              | UART0                     |                         | UART1                     |

| Two 8-bit counter/timers |                           |                         |                           |

| (Timer 0 only)           |                           |                         |                           |

## **Timer Clock Source**

- System clock divided by a factor

- 1

- 12

- External clock on a pin

- Counter operation

- Max f<sub>clk</sub>/4

#### R/W R/W R/W R/W R/W R/W R/W R/W Reset Value T4M T2M T1M T0M Reserved Reserved Reserved 00000000 Bit7 Bit6 Bit5 Bit3 Bit1 SFR Address: Bit4 Bit2 Bit0 0x8E UNUSED. Read = 0b, Write = don't care. Bit7: T4M: Timer 4 Clock Select. Bit6: This bit controls the division of the system clock supplied to Timer 4. This bit is ignored when the timer is in baud rate generator mode or counter mode (i.e. C/T4 = 1). 0: Timer 4 uses the system clock divided by 12. 1: Timer 4 uses the system clock. T2M: Timer 2 Clock Select. Bit5: This bit controls the division of the system clock supplied to Timer 2. This bit is ignored when the timer is in baud rate generator mode or counter mode (i.e. C/T2 = 1). 0: Timer 2 uses the system clock divided by 12. 1: Timer 2 uses the system clock. Bit4: T1M: Timer 1 Clock Select. This bit controls the division of the system clock supplied to Timer 1. 0: Timer 1 uses the system clock divided by 12. 1: Timer 1 uses the system clock. Bit3: T0M: Timer 0 Clock Select. This bit controls the division of the system clock supplied to Counter/Timer 0. 0: Counter/Timer uses the system clock divided by 12. 1: Counter/Timer uses the system clock. Reserved. Read = 000b, Must Write = 000. Bits2-0:

#### Figure 22.1. CKCON: Clock Control Register

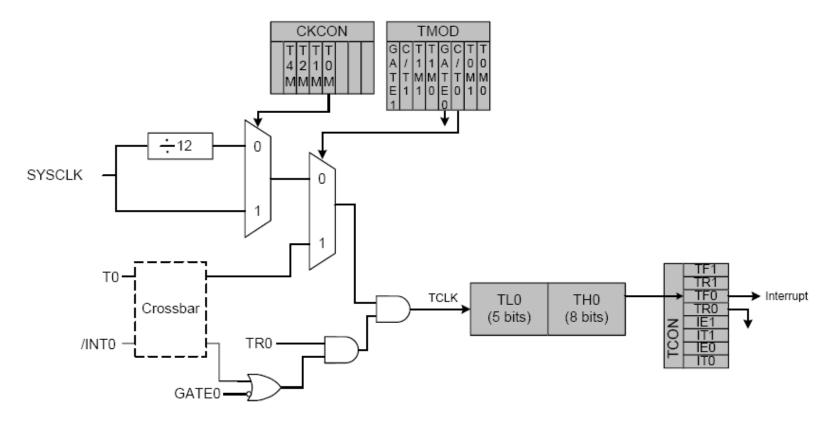

### Figure 22.2. T0 Mode 0 Block Diagram

| TR0    | GATE0     | /INT0 | Counter/Timer |

|--------|-----------|-------|---------------|

| 0      | X         | X     | Disabled      |

| 1      | 0         | X     | Enabled       |

| 1      | 1         | 0     | Disabled      |

| 1      | 1         | 1     | Enabled       |

| X = Dc | on't Care |       |               |

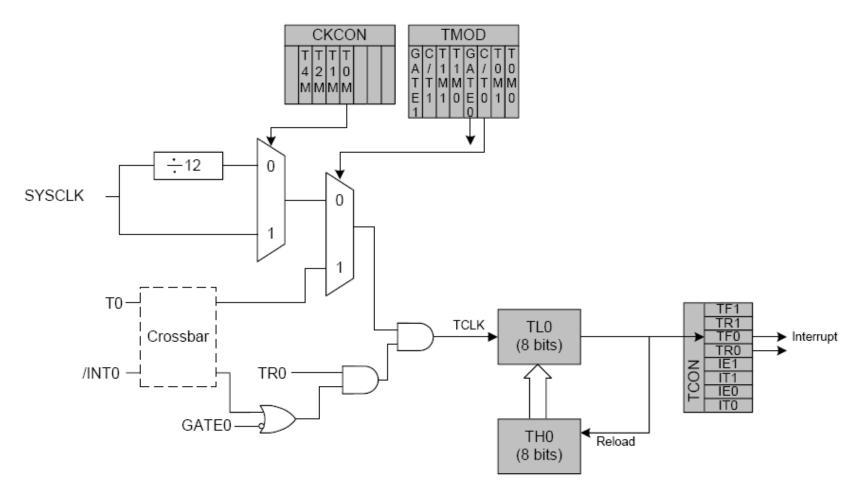

Figure 22.3. T0 Mode 2 (8-bit Auto-Reload) Block Diagram

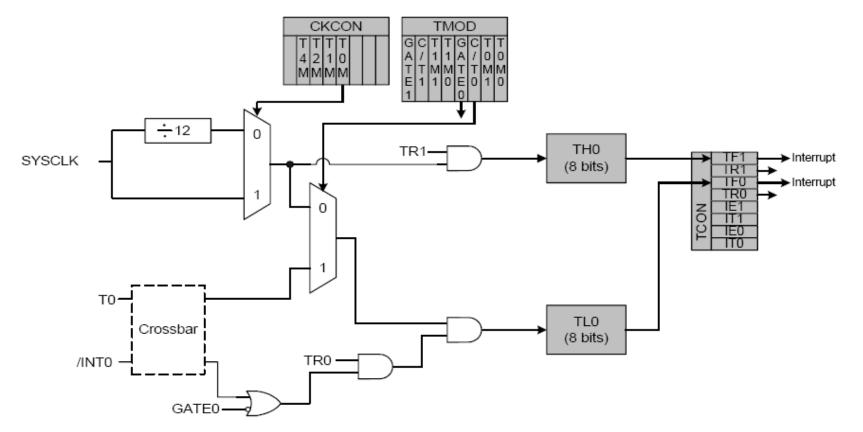

Figure 22.4. T0 Mode 3 (Two 8-bit Timers) Block Diagram

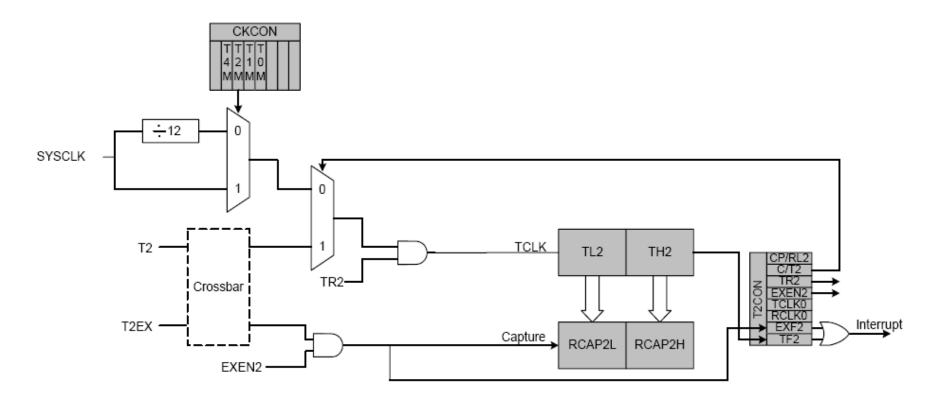

### Figure 22.11. T2 Mode 0 Block Diagram

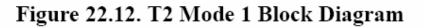

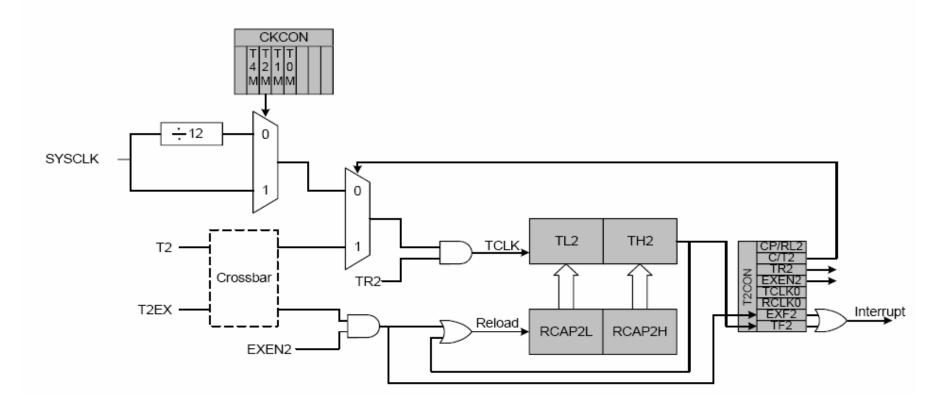

Figure 22.13. T2 Mode 2 Block Diagram

| Oscillator frequency (MHz) | Divide Factor | Timer 1 Load Value* | Resulting Baud Rate (Hz)** |  |  |

|----------------------------|---------------|---------------------|----------------------------|--|--|

| 25.0                       | 434           | 0xE5                | 57600 (57870)              |  |  |

| 25.0                       | 868           | 0xCA                | 28800                      |  |  |

| 24.576                     | 320           | 0xEC                | 76800                      |  |  |

| 24.576                     | 848           | 0xCB                | 28800 (28921)              |  |  |

| 24.0                       | 208           | 0XF3                | 115200 (115384)            |  |  |

| 24.0                       | 833           | 0xCC                | 28800 (28846)              |  |  |

| 23.592                     | 205           | 0xF3                | 115200 (113423)            |  |  |

| 23.592                     | 819           | 0xCD                | 28800 (28911)              |  |  |

| 22.1184                    | 192           | 0xF4                | 115200                     |  |  |

| 22.1184                    | 768           | 0xD0                | 28800                      |  |  |

| 18.432                     | 160           | 0xF6                | 115200                     |  |  |

| 18.432                     | 640           | 0xD8                | 28800                      |  |  |

| 16.5888                    | 144           | 0xF7                | 115200                     |  |  |

| 16.5888                    | 576           | 0xDC                | 28800                      |  |  |

| 14.7456                    | 128           | 0xF8                | 115200                     |  |  |

| 14.7456                    | 512           | 0xE0                | 28800                      |  |  |

| 12.9024                    | 112           | 0xF9                | 115200                     |  |  |

| 12.9024                    | 448           | 0xE4                | 28800                      |  |  |

| 11.0592                    | 96            | 0xFA                | 115200                     |  |  |

| 11.0592                    | 348           | 0xE8                | 28800                      |  |  |

| 9.216                      | 80            | 0xFB                | 115200                     |  |  |

| 9.216                      | 320           | 0xEC                | 28800                      |  |  |

| 7.3728                     | 64            | 0xFC                | 115200                     |  |  |

| 7.3728                     | 256           | 0xF0                | 28800                      |  |  |

| 5.5296                     | 48            | 0xFD                | 115200                     |  |  |

| 5.5296                     | 192           | 0xF4                | 28800                      |  |  |

| 3.6864                     | 32            | 0xFE                | 115200                     |  |  |

| 3.6864                     | 128           | 0xF8                | 28800                      |  |  |

| 1.8432                     | 16            | 0xFF                | 115200                     |  |  |

| 1.8432                     | 64            | 0xFC                | 28800                      |  |  |

Table 21.2. Oscillator Frequencies for Standard Baud Rates

\* Assumes SMOD1=1 and T1M=1.

\*\* Numbers in parenthesis show the actual baud rate.

### Interrupts

- A total of 22 interrupt sources with two priority levels.

- When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

- If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU begins execution of an interrupt service routine (ISR).

- If interrupts are not enabled, the interruptpending flag is ignored by the hardware and program execution continues as normal.

### Interrupts

- Interrupt vs. Polling strategies

- Interrupt condition

- Interrupt vector

- Interrupt enable

- Interrupt service routine

- Program flow remains the same after interrupt

| Interrupt Source             | Interrupt<br>Vector | Priority<br>Order | ' Pending Flag                      |     | Cleared by HW? | Enable<br>Flag     | Priority<br>Control |

|------------------------------|---------------------|-------------------|-------------------------------------|-----|----------------|--------------------|---------------------|

| Reset                        | 0x0000              | Top               | None                                | N/A | N/A            | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0 (/INT0) | 0x0003              | 0                 | IE0 (TCON.1)                        | Y   | Y              | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow             | 0x000B              | 1                 | TF0 (TCON.5)                        | Y   | Y              | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1 (/INT1) | 0x0013              | 2                 | IE1 (TCON.3)                        | Y   | Y              | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow             | 0x001B              | 3                 | TF1 (TCON.7)                        | Y   | Y              | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                        | 0x0023              | 4                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)      | Υ   |                | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2 Overflow (or EXF2)   | 0x002B              | 5                 | TF2 (T2CON.7)                       | Y   |                | ET2 (IE.5)         | PT2 (IP.5)          |

| Serial Peripheral Interface  | 0x0033              | 6                 | SPIF (SPI0CN.7)                     | Υ   |                | ESPI0<br>(EIE1.0)  | PSPI0<br>(EIP1.0)   |

| SMBus Interface              | 0x003B              | 7                 | SI (SMB0CN.3)                       | Υ   |                | ESMB0<br>(EIE1.1)  | PSMB0<br>(EIP1.1)   |

| ADC0 Window Comparator       | 0x0043              | 8                 | AD0WINT<br>(ADC0CN.2)               | Υ   |                | EWADC0<br>(EIE1.2) | PWADC0<br>(EIP1.2)  |

| Programmable Counter Array   | 0x004B              | 9                 | CF (PCA0CN.7)<br>CCFn<br>(PCA0CN.n) | Y   |                | EPCA0<br>(EIE1.3)  | PPCA0<br>(EIP1.3)   |

| Comparator 0 Falling Edge    | 0x0053              | 10                | CP0FIF<br>(CPT0CN.4)                |     |                | ECP0F<br>(EIE1.4)  | PCP0F<br>(EIP1.4)   |

| Comparator 0 Rising Edge     | 0x005B              | 11                | CPORIF<br>(CPT0CN.5)                |     |                | ECP0R<br>(EIE1.5)  | PCP0R<br>(EIP1.5)   |

| Comparator 1 Falling Edge    | 0x0063              | 12                | CP1FIF<br>(CPT1CN.4)                |     |                | ECP1F<br>(EIE1.6)  | PCP1F<br>(EIP1.6)   |

| Comparator 1 Rising Edge     | 0x006B              | 13                | CP1RIF<br>(CPT1CN.5)                |     |                | ECP1R<br>(EIE1.7)  | PCP1F<br>(EIP1.7)   |

| Timer 3 Overflow             | 0x0073              | 14                | TF3 (TMR3CN.7)                      |     |                | ET3<br>(EIE2.0)    | PT3<br>(EIP2.0)     |

| ADC0 End of Conversion       | 0x007B              | 15                | AD0INT<br>(ADC0CN.5)                | Υ   |                | EADC0<br>(EIE2.1)  | PADC0<br>(EIP2.1)   |

| Timer 4 Overflow             | 0x0083              | 16                | TF4 (T4CON.7)                       |     |                | ET4<br>(EIE2.2)    | PT4<br>(EIP2.2)     |

| ADC1 End of Conversion       | 0x008B              | 17                | AD1INT<br>(ADC1CN.5)                |     |                | EADC1<br>(EIE2.3)  | PADC1<br>(EIP2.3)   |

| External Interrupt 6         | 0x0093              | 18                | IE6 (P3IF.5)                        |     |                | EX6<br>(EIE2.4)    | PX6<br>(EIP2.4)     |

| External Interrupt 7         | 0x009B              | 19                | IE7 (P3IF.6)                        |     |                | EX7<br>(EIE2.5)    | PX7<br>(EIP2.5)     |

| UART1                        | 0x00A3              | 20                | RI1 (SCON1.0)<br>TI1 (SCON1.1)      |     |                | ES1                | PS1                 |

| External Crystal OSC Ready   | 0x00AB              | 21                | XTLVLD<br>(OSCXCN.7)                |     |                | EXVLD<br>(EIE2.7)  | PXVLD<br>(EIP2.7)   |

Table 12.4. Interrupt Summary

Figure 12.9. IE: Interrupt Enable

| R/W    | R/W                                               | R/W                          | R/W          | R/W           | R/W           | R/W           | R/W             | Reset Value     |  |  |  |  |

|--------|---------------------------------------------------|------------------------------|--------------|---------------|---------------|---------------|-----------------|-----------------|--|--|--|--|

| EA     | IEGF0                                             | ET2                          | ES0          | ET1           | EX1           | ET0           | EX0             | 00000000        |  |  |  |  |

| Bit7   | Bit6                                              | Bit5                         | Bit4         | Bit3          | Bit2          | Bitl          | Bit0            | SFR Address:    |  |  |  |  |

|        |                                                   |                              |              |               |               |               | (bit addressabl | e) 0xA8         |  |  |  |  |

| Bit7:  | EA: Enable Al                                     | 11 Interrupts                |              |               |               |               |                 |                 |  |  |  |  |

| 20117. | This bit global                                   | -                            |              | ternuots Wł   | en set to '0' | individual in | nternuot mas    | sk settings are |  |  |  |  |

|        | overridden.                                       | -,                           |              | r             |               |               | <u>-</u>        |                 |  |  |  |  |

|        | 0: Disable all i                                  | interrupt sou                | urces.       |               |               |               |                 |                 |  |  |  |  |

|        | 1: Enable each                                    | -                            |              | ts individual | mask setting  | t.            |                 |                 |  |  |  |  |

| Bit6:  | IEGF0: Gener                                      |                              |              |               |               | <i>,</i>      |                 |                 |  |  |  |  |

|        | This is a gener                                   |                              |              | nder softwa   | re control.   |               |                 |                 |  |  |  |  |

| Bit5:  | ET2: Enabler                                      |                              |              |               |               |               |                 |                 |  |  |  |  |

|        | This bit sets th                                  |                              | •            | 2 interrupt.  |               |               |                 |                 |  |  |  |  |

|        | 0: Disable Tin                                    | ier 2 interru                | pt.          | -             |               |               |                 |                 |  |  |  |  |

|        | 1: Enable inter                                   | rupt reques                  | ts generated | by the TF2 f  | lag (T2CON    | .7).          |                 |                 |  |  |  |  |

| Bit4:  |                                                   | ES0: Enable UARTO Interrupt. |              |               |               |               |                 |                 |  |  |  |  |

|        | This bit sets the masking of the UART0 interrupt. |                              |              |               |               |               |                 |                 |  |  |  |  |

|        | 0: Disable UA                                     | RT0 interru                  | pt.          |               |               |               |                 |                 |  |  |  |  |

|        | 1: Enable UAI                                     | RT0 interrup                 | ot.          |               |               |               |                 |                 |  |  |  |  |

| Bit3:  | ET1: Enable T                                     |                              |              |               |               |               |                 |                 |  |  |  |  |

|        | This bit sets th                                  | e masking o                  | of the Timer | 1 interrupt.  |               |               |                 |                 |  |  |  |  |

|        | 0: Disable all                                    | Timer 1 inte                 | rrupt.       |               |               |               |                 |                 |  |  |  |  |

|        | 1: Enable inter                                   | rupt reques                  | ts generated | by the TF1 i  | lag (TCON.7   | 7).           |                 |                 |  |  |  |  |

| Bit2:  | EX1: Enable F                                     |                              | -            |               |               |               |                 |                 |  |  |  |  |

|        | This bit sets th                                  | -                            |              | terrupt 1.    |               |               |                 |                 |  |  |  |  |

|        | 0: Disable exte                                   |                              | •            |               |               |               |                 |                 |  |  |  |  |

|        | 1: Enable inter                                   |                              | ~            | by the /INT   | l pin.        |               |                 |                 |  |  |  |  |

| Bit1:  | ET0: Enable T                                     |                              | -            |               |               |               |                 |                 |  |  |  |  |

|        | This bit sets th                                  |                              |              | 0 interrupt.  |               |               |                 |                 |  |  |  |  |

|        | 0: Disable all                                    |                              |              |               |               |               |                 |                 |  |  |  |  |

|        | 1: Enable inter                                   |                              |              | by the TF0 f  | lag (TCON.5   | 5).           |                 |                 |  |  |  |  |

| Bit0:  | EX0: Enable E                                     |                              | •            | -             |               |               |                 |                 |  |  |  |  |

|        | This bit sets th                                  | -                            |              | terrupt 0.    |               |               |                 |                 |  |  |  |  |

|        | 0: Disable exte                                   |                              | •            |               |               |               |                 |                 |  |  |  |  |

|        | 1: Enable inter                                   | rupt reques                  | ts generated | by the /INT   | ) pin.        |               |                 |                 |  |  |  |  |

| R/W      | R/W              | R/W           | R/W             | R/W           | R/W             | R/W  | R/W              | Reset Value  |

|----------|------------------|---------------|-----------------|---------------|-----------------|------|------------------|--------------|

| -        | -                | PT2           | PS0             | PT1           | PX1             | PT0  | PX0              | 00000000     |

| Bit7     | Bit6             | Bit5          | Bit4            | Bit3          | Bit2            | Bitl | Bit0             | SFR Address: |

|          |                  |               |                 |               |                 |      | (bit addressable | ) 0xB8       |

| Bits7-6: | UNUSED. Re       | ad = 11b, W   | /rite = don't o | are.          |                 |      |                  |              |

| Bit5:    | PT2: Timer 2     | Interrupt Pri | iority Control  | L.            |                 |      |                  |              |

|          | This bit sets th | ne priority o | f the Timer 2   | interrupt.    |                 |      |                  |              |

|          | 0: Timer 2 inte  | errupt priori | ty determine    | d by default  | priority order  |      |                  |              |

|          | 1: Timer 2 inte  | errupts set t | o high priorit  | y level.      |                 |      |                  |              |

| Bit4:    | PS0: UART0       | Interrupt Pri | iority Control  | L.            |                 |      |                  |              |

|          | This bit sets th | ne priority o | f the UART0     | interrupt.    |                 |      |                  |              |

|          | 0: UART0 inte    | errupt priori | ty determine    | d by default  | priority order  |      |                  |              |

|          | 1: UART0 inte    | errupts set t | o high priorit  | y level.      |                 |      |                  |              |

| Bit3:    | PT1: Timer 1     | Interrupt Pri | iority Control  | L.            |                 |      |                  |              |

|          | This bit sets th | ne priority o | f the Timer 1   | interrupt.    |                 |      |                  |              |

|          | 0: Timer 1 inte  | errupt priori | ty determine    | d by default  | priority order  |      |                  |              |

|          | 1: Timer 1 inte  | errupts set t | o high priorit  | y level.      |                 |      |                  |              |

| Bit2:    | PX1: External    | Interrupt 1   | Priority Con    | trol.         |                 |      |                  |              |

|          | This bit sets th | ne priority o | f the Externa   | l Interrupt 1 | interrupt.      |      |                  |              |

|          | 0: External Int  | terrupt 1 pri | ority determi   | ned by defa   | alt priority or | ler. |                  |              |

|          | 1: External Int  | terrupt 1 set | to high prior   | ity level.    |                 |      |                  |              |

| Bit1:    | PT0: Timer 0     | Interrupt Pri | iority Control  | L.            |                 |      |                  |              |

|          | This bit sets th |               |                 |               |                 |      |                  |              |

|          | 0: Timer 0 inte  | errupt priori | ty determine    | d by default  | priority order  |      |                  |              |

|          | 1: Timer 0 inte  | errupt set to | high priority   | level.        |                 |      |                  |              |

| Bit0:    | PX0: External    | Interrupt 0   | Priority Con    | trol.         |                 |      |                  |              |

|          | This bit sets th | ne priority o | f the Externa   | l Interrupt 0 | interrupt.      |      |                  |              |

|          | 0: External Int  |               | -               | -             | alt priority or | ler. |                  |              |

|          | 1: External Int  | termint 0 set | to high prior   | ity level     |                 |      |                  |              |

#### Figure 12.10. IP: Interrupt Priority

## Keil Development Tool

- Platform for microcontroller development

- You can program in C or even C++

- You call SFRs by their name

- Interfaces directly to JTAG cables

- Can generate HEX code for programmers

## **Programming Hints**

- Use #define to make your code readable

- Use #IF to make different versions with same code

- Macros vs. subroutines

- Assembly vs. C

- Real-Time Operating System (RTOS)