### Introduction to VHDL

Modules #6 and #7 Digilent Inc. Course

## Data Selectors / Multiplexers

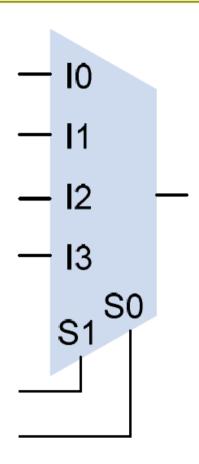

| S1 | S0 | Υ          |

|----|----|------------|

| 0  | 0  | 10         |

| 0  | 1  | <b>I</b> 1 |

| 1  | 0  | 12         |

| 1  | 1  | 13         |

4:1 mux truth table

Mux circuit symbol

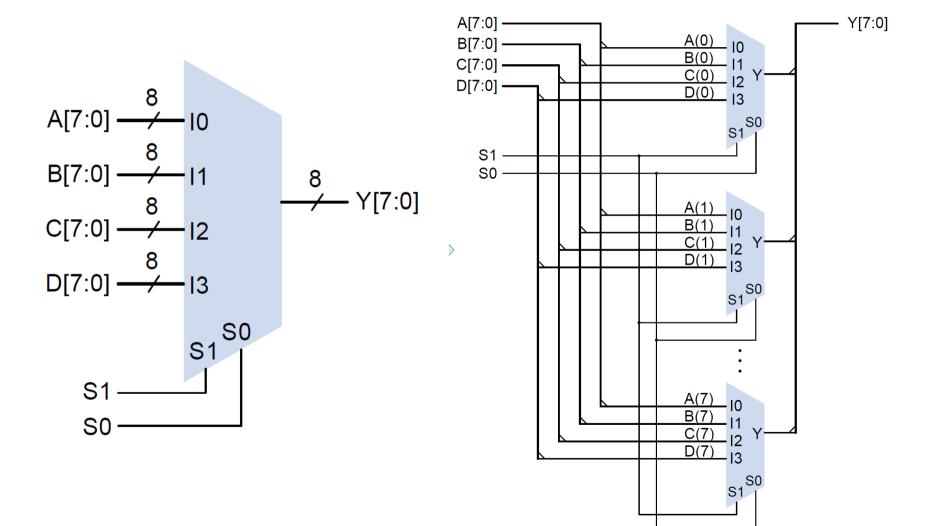

## Bus Multiplexer

## MUX VHDL Example: Selected Signal Assignment

```

entity mux_select is

port (13, 12, 11, 10: in std_logic;

sel : in std_logic_vector (1 downto 0);

Y : out std_logic);

end mux_select;

architecture behavioral of mux_select is

Begin

with sel select

Y <= 10 when "00";

I1 when "01";

I2 when "10";

I3 when "others;

end behavioral:

```

## Bus MUX VHDL Example: Selected Signal Assignment

```

entity busmux select is

port (I3, I2, I1, I0: in std_logic_vector (7 downto 0);

: in std_logic_vector (1 downto 0);

: outstd_logic_vector (7 downto 0));

end busmux_select;

architecture behavioral of busmux_select is

Begin

with sel select

Y <= 10 when "00";

I1 when "01";

12 when "10";

13 when "others;

end behavioral;

```

## More Complex MUX VHDL: Conditional Assignment

```

entity mux cond is

port (A, B, C : in std_logic_vector (7 downto 0);

Sel : in std_logic_vector (1 downto 0);

: outstd logic vector (7 downto 0));

end mux cond;

architecture behavioral of mux cond is

Begin

Y \le (A \text{ or not } C) \text{ when } (Sel = "00") \text{ else}

(A xor B) when (Sel = "01") else

not A when (Sel = "10") else

(B nand C);

end behavioral;

```

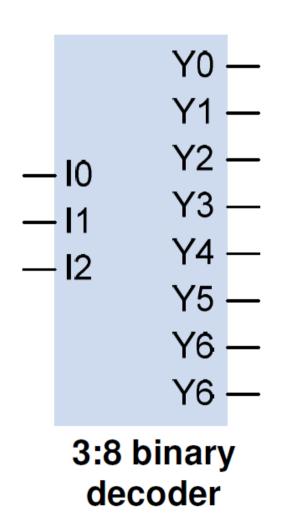

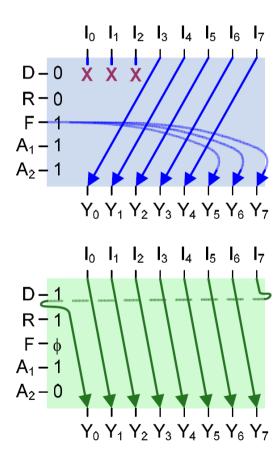

### Decoder

# Decoder VHDL Example: Selected Signal Assignment

```

entity decoder is

port (in: in std_logic_vector (1 downto 0);

out std logic vector (7 downto 0));

end decoder;

architecture behavioral of decoder is

Begin

with in select

Y <= "0001" when "00";

"0010" when "01";

"0100" when "10";

"1000" when "others;

end behavioral;

```

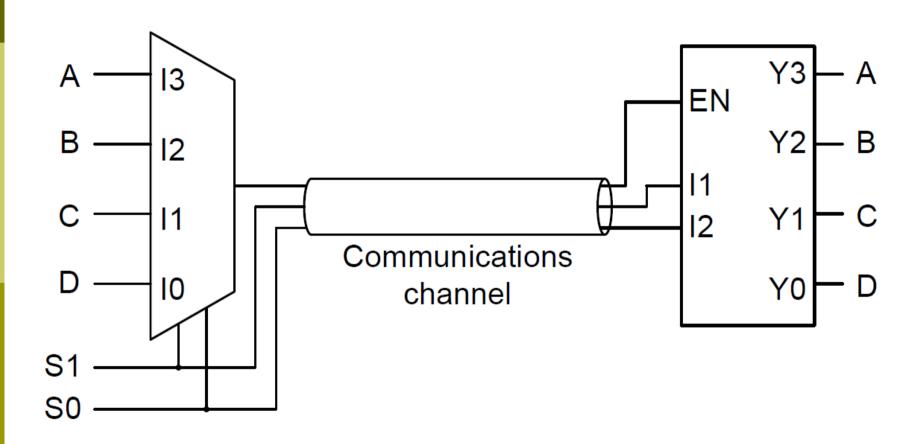

## DeMultiplexer (DeMUX)

#### **DeMUX VHDL Code**

Assignment: modify the code of a MUX to implement a DeMUX

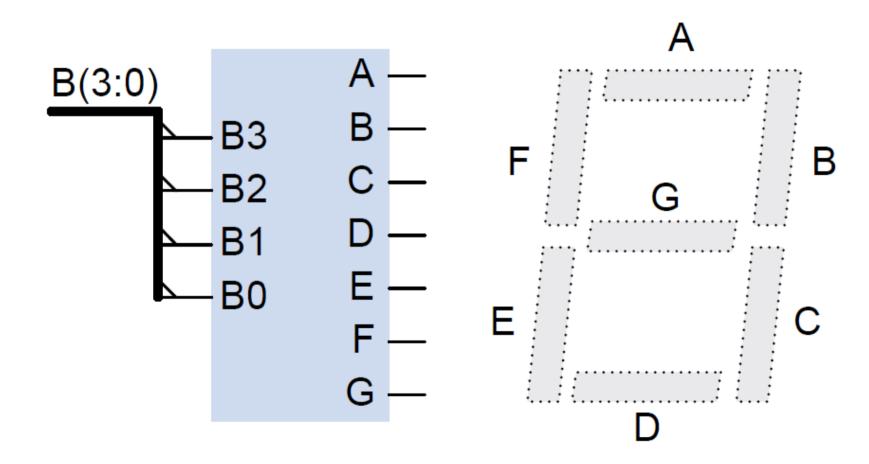

## 7-Segment Decoder

### 7-Segment Decoder VHDL Code

```

entity seven_seg_dec is

port (bin: in STD_LOGIC_VECTOR (3 downto 0);

segout: out STD LOGIC VECTOR (6 downto 0));

end seven_seg_dec;

architecture behavioral of seven_seg_dec is

begin

with bin select

segout <= "1111110" when "0000";

"0110000" when "0001";

"0000001" when others;

end behavioral;

```

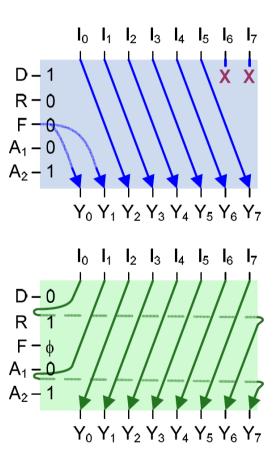

### **Priority Encoder**

```

entity encoder is

port (ein :

in std_logic;

in std_logic_vector (3 downto 0);

GS

eout, gs:

out std_logic;

out std_logic_vector (1 downto 0));

Y:

Y0

end encoder;

Y1

architecture Behavioral of encoder is

E<sub>OUT</sub>

Begin

eout <=ein and not I(3) and not I(2) and not I(1) and not I(0);

gs \leq ein and (I(3) or I(2) or I(1) or I(0));

Priority

Y(1) \le I(3) \text{ or } I(2);

Encoder

Y(0) \le I(3) \text{ or } I(1);

end Behavioral;

```

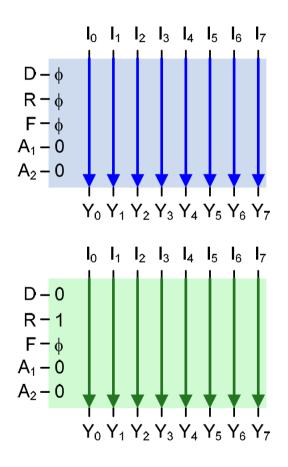

#### **Shifters**

#### **Shifters**

|   |   | D           |                       |                |                |       |

|---|---|-------------|-----------------------|----------------|----------------|-------|

| 0 | ф | φ<br>0<br>1 | 0                     | 0              | 0              | 0     |

| 1 | 0 | 0           | <b>l</b> <sub>2</sub> | $I_1$          | I <sub>0</sub> | 0     |

| 1 | 0 | 1           | 0                     | $I_3$          | $I_2$          | $I_1$ |

| 1 | 1 | 0           | I <sub>2</sub>        | $I_1$          | Ιo             | $I_3$ |

| 1 | 1 | 1           | I <sub>0</sub>        | l <sub>3</sub> | $I_2$          | $I_1$ |

Truth table for 4-bit shifter with shift/rotate left/right functions

### Shifters VHDL Example

```

entity my_shift is

r, d, en: in std_logic;

dout: out std_logic_vector (7 downto 0));

end my_shift;

architecture my_shift_arch of my_shift is

begin

dout <= "00000000" when en = '0' else

din(6 downto 0) \& din(7) when (r = '1' and d = '0') else

din(0) \& din(7 downto 1) when (r = '1' and d = '1') else

din(6 downto 0) & '0' when (r = '0' and d = '0') else

'0' & din(7 downto 1);

end my_shift_arch;

```

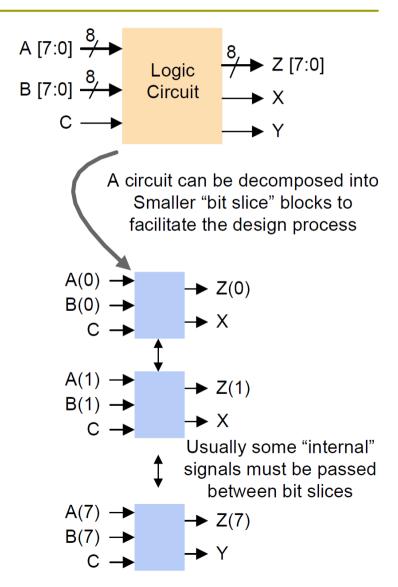

### Bit-Slice Design Method

- Consider a circuit that works on a pair of bits

- Goal is to create a circuit that can simply be replicated N times

- once for each bit

- Some circuits defy this approach

- Information passing between adjacent bits

### Comparators

```

Magnitude

Comparator

entity my_comp is

port ( A, B : in std_logic_vector (7 downto 0);

gt, It: inout std_logic;

eq : out std_logic);

end my_comp;

architecture behavioral of my_comp is

Begin

gt <= '1' when A > B else '0';

It <= '1' when A < B else '0';

eq <= not gt and not lt;

end behavioral;

```

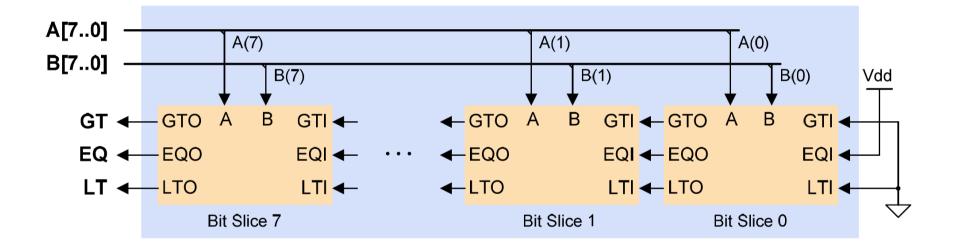

# Comparator Bit-Slice Design

|          | bit 7               |   |   |   |     | bit 2 |   | bit 0              |

|----------|---------------------|---|---|---|-----|-------|---|--------------------|

|          | <b>\undersigned</b> |   |   |   | _ [ |       |   | <b>\rightarrow</b> |

| A[7:0] → | 1                   | 0 | 0 | 1 | 1   | 1     | 1 | 1                  |

|          |                     |   |   |   |     |       |   |                    |

| B[7:0] → | 1                   | 0 | 0 | 1 | 1   | 0     | 1 | 1                  |

| Operand inputs |     | Inputs from<br>neighboring<br>slices |        |                        | Bit-sli                   | ice ou                     | tputs                                  |

|----------------|-----|--------------------------------------|--------|------------------------|---------------------------|----------------------------|----------------------------------------|

| An             | Bn  | GTI                                  | LTI    | EQI                    | GTO                       | LTO                        | EQO                                    |

| 0              | 0   | 1                                    | 0      | 0                      | 1                         | 0                          | 0                                      |

| 0              | 0   | 0                                    | 1      | 0                      | 0                         | 1                          | 0                                      |

| 0              | 0   | 0                                    | 0      | 1                      | 0                         | 0                          | 1                                      |

| 0              | 1   | φ                                    | φ      | φ                      | 0                         | 1                          | 0                                      |

| 1              | 0   | φ                                    | φ      | φ                      | 1                         | 0                          | 0                                      |

| 1              | 1   | 1                                    | Ó      | Ó                      | 1                         | 0                          | 0                                      |

| 1              | 1   | 0                                    | 1      | 0                      | 0                         | 1                          | 0                                      |

| 1              | 1   | 0                                    | 0      | 1                      | 0                         | 0                          | 1                                      |

|                | inp | inputs                               | inputs | inputs neighbor slices | inputs neighboring slices | inputs neighboring Bit-sli | inputs neighboring slices Bit-slice ou |

## Comparator Bit-Slice Design

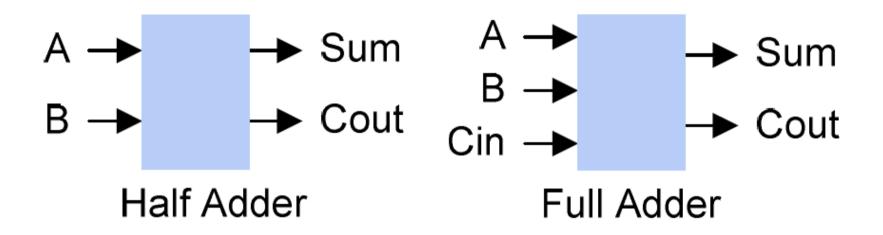

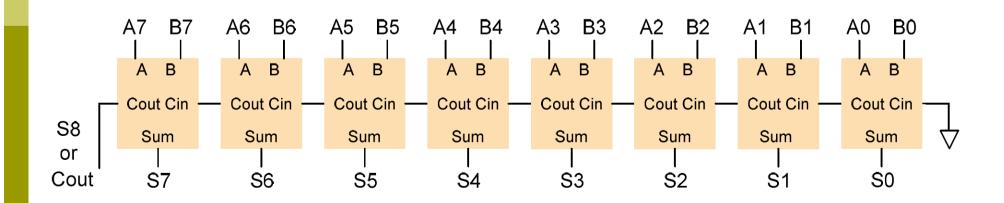

#### Adders

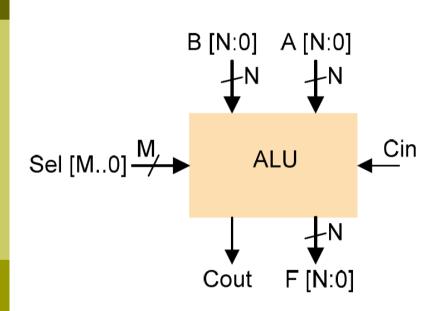

## Arithmetic and Logic Unit (ALU)

| Op Code | Function  |  |  |

|---------|-----------|--|--|

| 000     | A PLUS B  |  |  |

| 001     | A PLUS 1  |  |  |

| 010     | A MINUS B |  |  |

| 011     | 0         |  |  |

| 100     | A XOR B   |  |  |

| 101     | Α'        |  |  |

| 110     | A OR B    |  |  |

| 111     | A AND B   |  |  |

### 8-Bit, 4-Function ALU VHDL

```

entity ALU is

port (A, B: in std_logic_vector (7 downto 0);

Sel: in std logic vector (1 downto 0);

: out std logic vector (7 downto 0));

end ALU;

architecture behavioral of ALU is

Begin

With sel select

Y \le (A + B) when "00",

(A + "00000001") when "01",

(A or B) when "10",

(A and B) when others;

end behavioral;

```

## Assignment

- □ Lab Project P6

- Do only on Xilinx Webpack

- Simulate to show results

- No Digilent board demo is necessary